Halbleiter-Testplatinen: Qualitätssicherung im Chiptest

Schlüsselwörter: Halbleitertestplatine

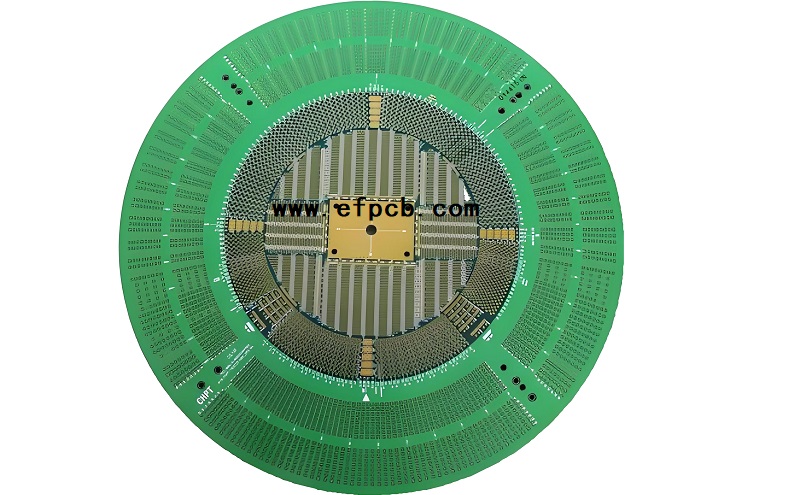

Das Halbleiterproduktionsgebiet umfasst vier wesentliche Zyklen: Halbleiterdesign, Waferbearbeitung, Waferverpackung und Halbleitertest. Das Testsystem wird in vier Kategorien unterteilt: Wafertest, Endprodukttest, Systemleveltest und Burn-in-Test. Testkarten, Lastplatinen und Burn-in-Platinen (Napkin) sind einige der Leiterplatten, die mit Halbleitertestplatinen verwendet werden. Es handelt sich um ein maßgeschneidertes Produkt, und die entsprechende Leiterplatte muss speziell angefertigt werden, um dem Chipdesign für den Test zu entsprechen.

Diese Leiterplatten werden als Halbleitertestplatinen bezeichnet. Sie sind ein grundlegendes Testverbrauchsmaterial nach der Chipverpackung. Sie werden üblicherweise während der Ausbeutetestphase eingesetzt. Es ist möglich, unvollständige Chips auszusortieren und die Kosten des Back-End-Prozesses zu senken, indem bewertet wird, ob die Chipfunktion, Geschwindigkeit, Zuverlässigkeit, Stromverbrauch und andere Eigenschaften normal sind. So wird Abfall vermieden und verhindert, dass Endprodukte aufgrund fehlerhafter integrierter Schaltkreise verworfen werden.

Testlastplatine: Eine mechanische und elektrische Schnittstelle, die Testgeräte mit dem zu testenden Gerät verbindet. Sie wird hauptsächlich im Ausbeutetest nach der IC-Verpackung am Back-End der Halbleiterproduktion verwendet. In dieser Testphase können beschädigte Teile entfernt werden, um zu verhindern, dass zukünftige elektrische Geräte aufgrund defekter ICs entsorgt werden.

Testkarte: Die Testkarte verbindet den Testautomaten mit dem Die-Pad während des CP-Tests.

Sie wird häufig als physikalische Schnittstelle zur Lastplatine verwendet. Unter bestimmten Bedingungen verbindet sich die Testkarte über einen Stecker oder eine andere Schnittstellenschaltung mit der Lastplatine. Vor dem Wafer-Sägen kann die Waferqualität mittels eines PCs überprüft werden, um Verpackungskosten für beschädigte Teile zu vermeiden.

Burn-in-Platine (Burn-in Load Board): Nach Abschluss des Verpackungstests wird der IC einem Alterungstest unter genauen Betriebsbedingungen und Zeitvorgaben unterzogen, um seine Zuverlässigkeit sicherzustellen. Die Burn-in-Platine ist eine Leiterplatte, die zum Testen der Alterung integrierter Schaltkreise verwendet wird.

Interposer: Das Signal der Testkarte wird durch die Zwischenschicht des Interposers übersetzt, wodurch der Testkopf das Signal erfassen und erfolgreich zur Interpretation an den Testautomaten weiterleiten kann.

Da die Halbleitertechnologie sich rasant weiterentwickelt, nehmen auch die mit dem Testen verbundenen Herausforderungen zu. Hersteller versuchen ständig, weiterentwickelte Halbleitertestplatinen zu schaffen, die in der Lage sind, höhere Geschwindigkeiten, kleinere Strukturfaktoren und größere Komplexität in Halbleiterbauelementen zu bewältigen. Darüber hinaus führt die Einführung von künstlicher Intelligenz (KI) in den Halbleitertest zu einer zunehmenden Betonung von Automatisierung und prädiktiver Analyse, um Produktivität und Genauigkeit zu steigern.

Neben diesen Fortschritten ergeben sich jedoch auch Herausforderungen wie Kosten, Skalierbarkeit und Kompatibilität mit aufkommenden Technologien. Die Abwägung zwischen der Notwendigkeit umfassender Tests und dem Druck von Time-to-Market sowie Kostenbeschränkungen bleibt ein fortwährendes Problem für Halbleiterhersteller.

- 1Was ist Ultra HDI-Leiterplatten ?

- 2HDI-Leiterplatten Marktaussichten 2025: Zukunft Perspektiven, Wachstumsanalyse & Innovationen

- 3Leiterplatte Vollständiger Leitfaden (2024)

- 4Mehrschichtige Rigid- flexible Leiterplatte : Leiterplatten Innovationen in Blind/Begraben über Strukturen

- 5HDI Leiterplattendesign Umfassender Leitfaden: Mastering High Density Interconnect Technology im Jahr 2025

- 6Häufige Ausfallmodi von Rigid flexible leiterplatten

- 7Was ist IPC 4761 Typ VII Via in Pad Leiterplatten ?

- 8Wie man wählt a schnelldrehung HDI-Leiterplatte Hersteller?

- 9HDI-Leiterplatte Hersteller | Umfassender Leitfaden 2025

- 10Dynamisches Biegen VS Statisches Biegen flexible Leiterplatte Gestaltung

- Skype-ID: shawnwang2006

- Telefon: +86-755-23724206

- E-Mail-Adresse: sales@efpcb.com

- Schneller Kontakt