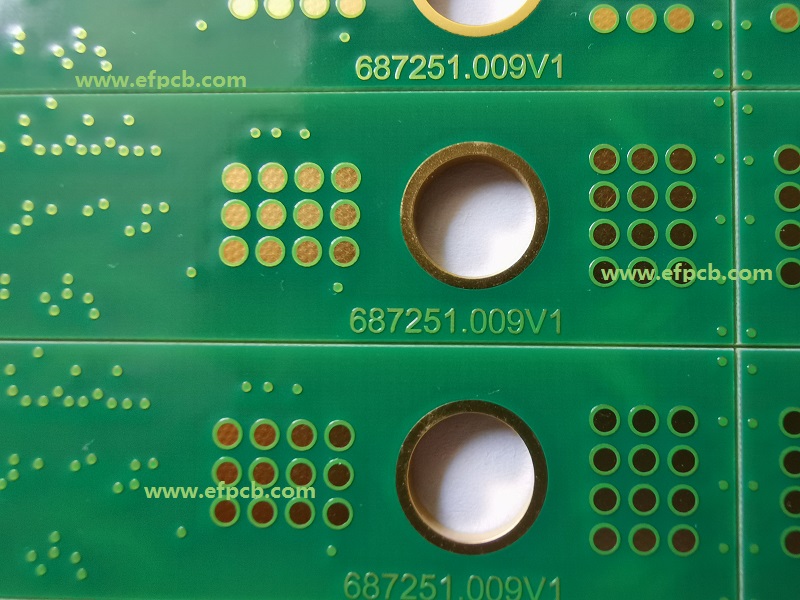

Die Bedeutung und der Standard der Via-on-PAD-Technologie für Leiterplatten

Warum benötigen Leiterplatten Via on PAD Design

Im Design von Leiterplatten (PCB) ist das Via on PAD Design eine spezielle Methode, die hauptsächlich die folgenden Funktionen erfüllt:

1. Hohe Verdrahtungsdichte-Anforderungen erfüllen

Verdrahtungsraum vergrößern

Mit der Entwicklung von Miniaturisierung und Multifunktionalität elektronischer Produkte wird die Dichte elektronischer Komponenten auf der Leiterplatte immer höher, und der Verdrahtungsraum wird extrem begrenzt.

Das Via on PAD Design kann durch das Setzen von Durchkontaktierungen auf dem Pad im begrenzten ebenen Raum die elektrische Verbindung zwischen verschiedenen Lagen realisieren, um mehr Pfadoptionen für die Verdrahtung zu bieten und den Verdrahtungsraum effektiv zu vergrößern.

Zum Beispiel im Motherboard-Design einiger High-End-Smartphones: Aufgrund der Integration vieler Funktionsmodule ist die Komponentendichte sehr hoch, und der Einsatz von Via on PAD Design kann die komplexen Verdrahtungsanforderungen erfüllen, ohne die Leiterplattengröße zu erhöhen.

Komplexe Schaltungsverbindungen realisieren

In einigen komplexen Schaltungsdesigns kann es notwendig sein, die Verbindung zwischen mehreren verschiedenen Netzen zu realisieren, aber die traditionelle Verdrahtungsmethode kann die Anforderungen nicht erfüllen.

Via on PAD Design kann durch das Setzen von Durchkontaktierungen an Schlüsselknoten verschiedene Netze verbinden, um komplexe Schaltungsfunktionen zu realisieren.

Zum Beispiel in Hochgeschwindigkeits-Digitalschaltungen: Um die Integrität des Signals zu gewährleisten, muss die Impedanz des Signals streng kontrolliert werden. Durch das Design von Via on PAD kann an einer bestimmten Position eine Erdungsdurchkontaktierung eingeführt werden, um den Referenzebenenwechsel des Signals zu realisieren, um so die Impedanz des Signals anzupassen und die Anforderungen der Hochgeschwindigkeitssignalübertragung zu erfüllen.

2. Elektrische Leistung verbessern

Signalübertragungsimpedanz reduzieren

Wenn das Signal auf der Leiterplatte übertragen wird, führt die Diskontinuität der Impedanz zu Problemen wie Signalreflexion und -dämpfung, was die Signalqualität beeinträchtigt.

Das Via on PAD Design kann durch Optimierung der Position, Größe und Form der Durchkontaktierung die Impedanzdiskontinuität auf dem Signalübertragungspfad reduzieren, um so die Signalübertragungsimpedanz zu verringern und die Integrität des Signals zu verbessern.

Zum Beispiel bei der Hochgeschwindigkeits-Differenzialsignalübertragung: Durch angemessenes Design der Position und Abstände der Pad-Durchkontaktierungen kann die Impedanz des Differenzialpaares besser angeglichen, das Übersprechen zwischen Differenzialsignalen reduziert und die Übertragungsqualität des Signals verbessert werden.

Elektromagnetische Störungen reduzieren

In elektronischen Produkten sind elektromagnetische Störungen ein häufiges Problem, das den normalen Betrieb der Schaltung beeinträchtigt.

Via on PAD Design kann die Auswirkungen elektromagnetischer Störungen reduzieren, indem es empfindliche Signale von Störquellen isoliert.

Zum Beispiel in einer Leiterplatte, auf der analoge und digitale Schaltungen koexistieren: Ein Via on PAD kann zwischen analoger Masse und digitaler Masse gesetzt werden, um die Teilung der Masseebene zu realisieren und die Störung digitaler Schaltungen auf analoge Schaltungen zu reduzieren.

3. Kühlleistung verbessern

Kühlkanäle bereitstellen

Mit zunehmender Leistungsdichte elektronischer Komponenten ist die Wärmeableitung zu einem der Schlüsselfaktoren geworden, die die Zuverlässigkeit elektronischer Produkte beeinflussen.

Via on PAD Design kann einen Wärmeableitungskanal auf der Leiterplatte bilden, um die Wärme vom wärmeerzeugenden Element zur Kühlschicht oder zum externen Kühlkörper zu übertragen und so die Kühleffizienz zu verbessern.

Zum Beispiel kann im Leiterplatten-Design von Hochleistungs-LED-Beleuchtungskörpern durch das Anordnen von Via on PAD auf dem LED-Pad die von der LED erzeugte Wärme schnell an die Wärmeableitungsschicht der Leiterplatte übertragen werden, was die Arbeitstemperatur der LED senkt und ihre Zuverlässigkeit und Lebensdauer verbessert.

Gleichmäßige Wärmeverteilung

Auf einigen großflächigen Leiterplatten kann ungleichmäßige Wärmeableitung zu örtlich übermäßiger Temperatur führen, was die Leistung und Lebensdauer elektronischer Komponenten beeinträchtigt.

Das Via on PAD-Design kann durch eine vernünftige Verteilung der Durchkontaktierungen die Wärme gleichmäßiger auf der Leiterplatte verteilen und so das Problem lokaler Überhitzung vermeiden.

Zum Beispiel werden im Design großer Leiterplatten wie Server-Hauptplatinen typischerweise eine große Anzahl von Via on PAD verwendet, um die Wärmeableitungsleistung zu optimieren und sicherzustellen, dass die Temperatur der gesamten Platine innerhalb eines sicheren Bereichs liegt.

4. An besondere Verpackungsanforderungen anpassen

Erfüllung von BGA und anderen Verpackungsformen

Ball Grid Array (BGA)-Verpackung ist eine gängige Form der integrierten Schaltkreisverpackung mit einer großen Anzahl von Anschlüssen und geringem Abstand, was hohe Anforderungen an das Leiterplatten-Design stellt.

Das Via on PAD-Design kann für BGA-verpackte Chips eine gute elektrische Verbindung und Wärmeableitungskanäle bieten und die Anforderungen an hohe Dichte und hohe Leistung erfüllen.

Zum Beispiel werden im Design einiger Hochleistungs-Computer-Hauptplatinen und Grafikkarten BGA-verpackte Chips weit verbreitet eingesetzt, und das Via on PAD-Design wird zu einem unverzichtbaren Bestandteil.

Unterstützung der Installation spezieller Komponenten

In einigen speziellen Anwendungsszenarien müssen möglicherweise elektronische Komponenten mit besonderen Formen oder Größen installiert werden, während das traditionelle Leiterplatten-Design die Anforderungen möglicherweise nicht erfüllen kann.

Das Via on PAD-Design kann gemäß den Installationsanforderungen spezieller Komponenten angepasst werden, um zuverlässige Verbindung und Befestigung für diese speziellen Komponenten zu bieten.

Zum Beispiel kann es in einigen industriellen Steuergeräten notwendig sein, große Kühlkörper oder induktive Komponenten zu installieren. Durch das Anordnen von Via on PAD auf der Leiterplatte können diese Komponenten fest installiert und gut verbunden werden.

Was ist der Via on PAD-Standard bitte?

Der akzeptable Standard für das Via on PAD-Design umfasst hauptsächlich die folgenden Aspekte:

1. Elektrische Leistung

Kontinuität

Via on PAD muss eine gute elektrische Kontinuität gewährleisten. Wir können den Widerstandswert mit einem Multimeter oder einem speziellen Kontinuitätstester testen. Der Widerstandswert muss unseren Designvorgaben entsprechen.

Zum Beispiel sollte für gewöhnliche digitale Schaltungen der Durchgangswiderstand des Via on PAD weniger als 50 Milliohm betragen; Für hochpräzise analoge Schaltungen oder Hochgeschwindigkeitssignal-Übertragungsleitungen ist ein noch niedrigerer Durchgangswiderstand erforderlich, möglicherweise weniger als 10 Milliohm.

Impedanzkontrolle

Für Hochgeschwindigkeits-Digitalschaltungen und HF-Schaltungen muss die Impedanz des Via on PAD den Designanforderungen entsprechen. Wir verwenden im Allgemeinen Impedanzmessgeräte, um den Impedanzwert zu testen, um sicherzustellen, dass die Via on PAD-Qualität unter unserer Kontrolle liegt und der Impedanzwert innerhalb des spezifizierten Toleranzbereichs liegt.

Zum Beispiel sollte für eine 50-Ohm-Übertragungsleitung die Impedanz des Via on PAD zwischen 45 und 55 Ohm kontrolliert werden.

Signalintegrität

Durch den Signalintegritätstest wird der Einfluss von Via on PAD auf die Signalübertragung bewertet.

Wir können die Wellenform, Amplitude, Anstiegszeit, Abfallzeit und andere Parameter des Signals mit Geräten wie Oszilloskop und Netzwerkanalysator überprüfen, um sicherzustellen, dass es keine deutliche Verzerrung, Dämpfung oder Reflexion gibt, wenn das Signal das Via on PAD passiert.

Zum Beispiel wird für Hochgeschwindigkeits-Digitalsignale gefordert, dass sich die Anstiegs- und Abfallzeit des Signals nach dem Passieren des Via on PAD um nicht mehr als 10% ändert; Für HF-Signale wird ein Reflexionsfaktor von weniger als -15 dB gefordert.

2. Mechanische Eigenschaften

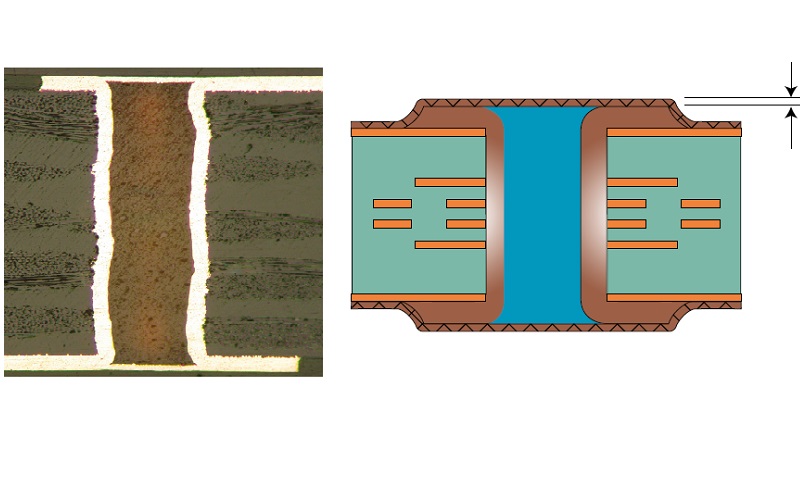

Lochwandqualität

Die Lochwand der Via auf der PAD soll glatt, frei von Rissen und Graten sein. Die Lochwand kann mit einem Mikroskop oder einem Elektronenmikroskop beobachtet werden, um Fehler zu überprüfen.

Die Rauheit der Lochwand soll den Anforderungen entsprechen. Allgemein wird eine Rauheit von weniger als 5 μm gefordert. Eine raue Lochwand beeinträchtigt die Zuverlässigkeit der elektrischen Verbindung und kann Signalübertragungsprobleme verursachen.

Bohrungsgenauigkeit

Der Durchmesser der Via auf der PAD soll den Designanforderungen entsprechen, die Toleranz liegt üblicherweise innerhalb von ± 0,05 mm. Wir müssen den Via-Durchmesser mit Röntgen- oder Mikroschnittgeräten messen, um sicherzustellen, dass er innerhalb des spezifizierten Bereichs liegt.

Die Position der Via auf der PAD soll genau sein, und die Abweichung vom Designplan soll innerhalb des spezifizierten Toleranzbereichs liegen. Koordinatenmessgeräte oder optische Prüfausrüstung können verwendet werden, um die Position der Via auf der PAD zu messen und sicherzustellen, dass ihre Positionsgenauigkeit den Anforderungen entspricht.

Zum Beispiel sollte für ein hochpräzises Leiterplatten-Design die Positionsabweichung der Via auf der PAD weniger als ± 0,05 mm betragen. Eine übermäßige Positionsabweichung kann das Layout der Schaltung und die Zuverlässigkeit der elektrischen Verbindung beeinflussen.

3. Zuverlässigkeit

Thermoschocktest

Die Leiterplatte wird einem Thermoschocktest unterzogen, um die Temperaturänderung elektronischer Produkte im tatsächlichen Gebrauch zu simulieren. Durch wiederholte Hochtemperatur- und Niedertemperaturwechsel wird überprüft, ob die Via auf der PAD Risse, Delaminierung, Ablösung oder andere Phänomene aufweist.

Zum Beispiel wird die Leiterplatte im Temperaturbereich von -55 °C bis 125 °C für 1000 Zyklen einem Thermoschocktest unterzogen, und die Via auf der PAD sollte frei von jeglichen Schäden sein.

Vibrationstest

Die Leiterplatte wird einem Vibrationstest unterzogen, um die Vibrationsumgebung elektronischer Produkte während des Transports und der Nutzung zu simulieren. Wir müssen überprüfen, ob sich die Via auf der PAD nach Anwendung einer bestimmten Frequenz und Amplitude von Vibrationen gelockert oder gebrochen hat.

Zum Beispiel führen wir einen zufälligen Vibrationstest mit einer Frequenz von 5-500 Hz und einer Beschleunigung von 5 g durch. Die Dauer beträgt 2 Stunden, und die Via auf der PAD sollte frei von jeglichen Schäden sein.

Lötbarkeitstest

Führen Sie einen Lötbarkeitstest an der Via auf der PAD durch, um ihre Leistung im Lötprozess zu überprüfen. Tauchen Sie die Leiterplatte in den Zinnbad, um die Via auf der PAD mit dem Lot in Kontakt zu bringen, und beobachten Sie, ob das Lot die Lochwand gut benetzen kann, um eine gleichmäßige Lötstelle zu bilden.

Zum Beispiel wird gefordert, dass die Steighöhe des Lots in der Via auf der PAD mindestens 75 % der Lochtiefe betragen soll und die Lötstelle glatt, frei von Poren, Nadellöchern und anderen Fehlern sein soll.

4. Sichtprüfung

Ebenheit

Die Oberfläche der Leiterplatte soll eben sein, und es soll keine deutliche Wölbung oder Vertiefung um die Via auf der PAD herum geben. Ein Ebenheitsmessgerät kann verwendet werden, um die Oberfläche der Leiterplatte zu messen und sicherzustellen, dass ihre Ebenheit den Anforderungen entspricht.

Zum Beispiel sollte für eine gewöhnliche Leiterplatte die Oberflächenebenheit weniger als ± 0,1 mm betragen. Für hochpräzise Leiterplatten ist eine höhere Ebenheit erforderlich, die möglicherweise innerhalb von ± 0,05 mm liegt.

Sauberkeit

Die Leiterplatte soll sauber gehalten werden, und es sollen keine Rückstände von Öl, Staub, Lötspänen oder anderen Verunreinigungen in der Via auf der PAD vorhanden sein. Die Sauberkeit der Via auf der PAD kann durch Sichtprüfung oder mikroskopische Beobachtung überprüft werden.

Wenn Verunreinigungen in der Via auf der PAD vorhanden sind, kann dies die Zuverlässigkeit der elektrischen Verbindung beeinträchtigen und sogar Fehler wie Kurzschlüsse verursachen.

Die Via auf der PAD auf der Leiterplatte soll klar gekennzeichnet sein, um die Produktion und Wartung zu erleichtern. Die Kennzeichnung soll Lochnummer, Netzwerkname, Lochgröße und andere Informationen enthalten.

Die Kennzeichnung kann mittels Siebdruck, Lasermarkierung usw. durchgeführt werden, und es soll sichergestellt werden, dass die Kennzeichnung klar, haltbar und nicht leicht abnutzbar oder ablösbar ist.

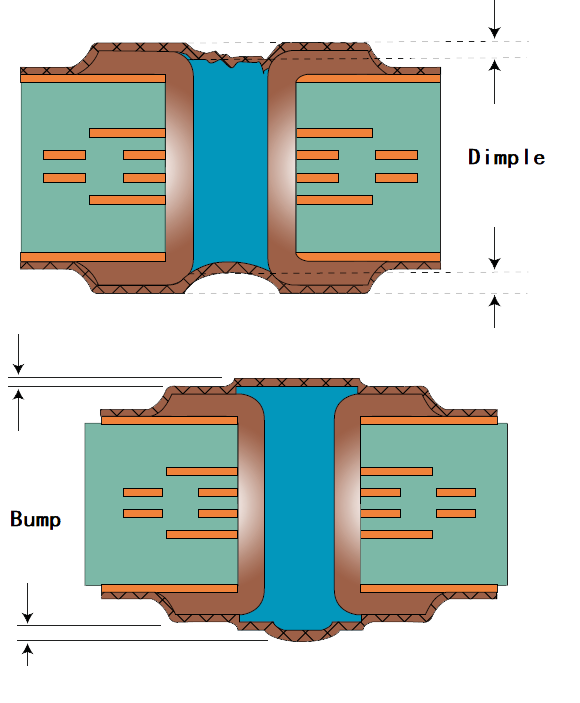

5. IPC-6012D oder IPC 4671 VII Standard für Via on Pad,

Haftung der metallisierten Beschichtung an der Via-Füllung und der Kupferfläche. Kupferdicke. Die Planarität zwischen dem Füllmaterial und der Kupferoberfläche. CTE-Unterschied zwischen Füllmaterial und Metallisierung, der zu Lufteinschlüssen führt (Schrumpfung des Füllmaterials). Eine weniger als 100%ige Via-Füllung kann zu einer zu dünnen metallisierten Abdeckung oder einer Delle führen, was ebenfalls eingeschlossene Luft verursachen kann, die zu Hohlräumen in BGA-Lötstellen führt. Poren in der metallisierten Beschichtung führen zu unlötbaren Bereichen einer Lötfläche, wenn das abgedeckte Via für eine BGA-Lötstelle vorgesehen ist. Ein reduziertes Lötvolumen ist ebenfalls ein Problem bei Dellen.

A: Idealer Zustand: ohne Delle oder Erhebung.

B: Mit Delle oder Erhebung.

|

|

Klasse I |

Klasse II |

Klasse III |

|

Abgedeckte Kupferdicke (µm) |

AABUS |

5 |

12 |

|

Delle max. (µm) |

AABUS |

127 |

76 |

|

Erhebung max. (µm) |

AABUS |

50 |

50 |

- 1Was ist Ultra HDI-Leiterplatten ?

- 2HDI-Leiterplatten Marktaussichten 2025: Zukunft Perspektiven, Wachstumsanalyse & Innovationen

- 3Leiterplatte Vollständiger Leitfaden (2024)

- 4Mehrschichtige Rigid- flexible Leiterplatte : Leiterplatten Innovationen in Blind/Begraben über Strukturen

- 5HDI Leiterplattendesign Umfassender Leitfaden: Mastering High Density Interconnect Technology im Jahr 2025

- 6Häufige Ausfallmodi von Rigid flexible leiterplatten

- 7Was ist IPC 4761 Typ VII Via in Pad Leiterplatten ?

- 8Wie man wählt a schnelldrehung HDI-Leiterplatte Hersteller?

- 9HDI-Leiterplatte Hersteller | Umfassender Leitfaden 2025

- 10Dynamisches Biegen VS Statisches Biegen flexible Leiterplatte Gestaltung

- Skype-ID: shawnwang2006

- Telefon: +86-755-23724206

- E-Mail-Adresse: sales@efpcb.com

- Schneller Kontakt