Was passiert in PAD Leiterplatten ?

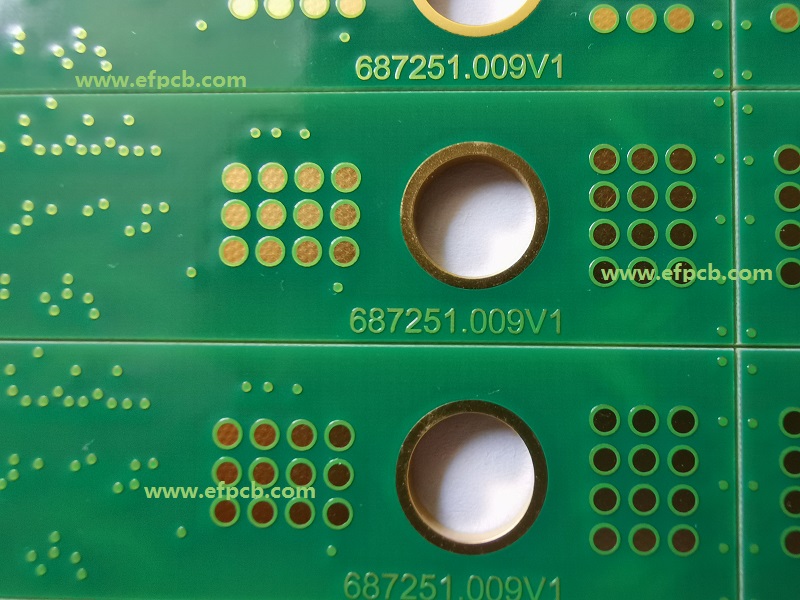

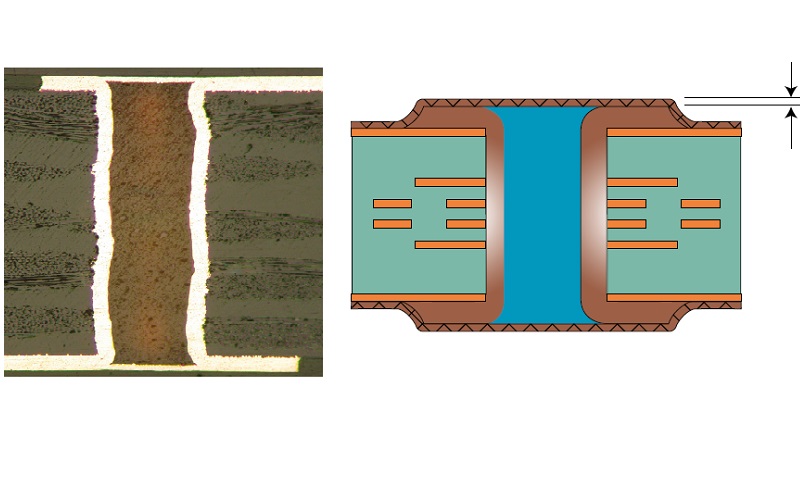

Ein über in PAD Leiterplatten Auch bekannt als "Via-on-PAD" Leiterplatten ", ist ein Leiterplatten die Vias aufweist, die sich direkt innerhalb des Lötpolsters eines Bauteils befinden / positionieren. Dies wird häufig mit hoher Dichte verwendet Leiterplatten Layouts, insbesondere wenn das Bauteil feinpitch ist (BGA etc.) oder einen kleinen Fußabdruck aufweist. Ziel von Via-in-Pad ist es, Platz zu sparen, die elektrische Leistung zu verbessern und die Routing in kleinen Pitch-Paketen zu vereinfachen. Dennoch erfordert dieses Verfahren eine Aufmerksamkeit auf die Prozesssteuerung während der Herstellung wegen der Gefahr, dass z.B. Lot in die Via fließt und das wiederum zu Lötfehlern führt. Um diese Probleme zu lösen, werden von den Herstellern weit verbreitet Verfahren wie z.B. durch Stecken oder Füllen mit leitendem oder nicht leitendem Material anschließend Planarisierung eingesetzt. Die korrekte Verarbeitung von Via-in-Pad ist eine Voraussetzung für eine zuverlässige Funktion und ermöglicht die Miniaturisierung elektronischer Geräte.

Warum brauchen wir Passe Via in PAD Leiterplatten ?

Die Verwendung von Via in PAD ist aufgrund der Optimierung und Verringerung der Konstruktionszeit nicht vermeidbar. Leiterplatten Mit Vias direkt auf dem PAD platziert, macht das vorgeschlagene Verfahren nicht nur eine bessere Nutzung des verfügbaren Raums, sondern es dämpft auch die Crosstalk, die erscheint, die zu einem besseren elektrischen Verhalten führt, insbesondere für die Hochdichte und Hochfrequenz-Designs. Es erleichtert auch die Routing, indem die Belastung von zusätzlichen Schichten oder Schwierigkeiten über Strukturen beseitigt wird, wodurch die Produktionskosten und die Anzahl der Konstruktionsiterationen gesenkt werden. Via in PAD Leiterplatten ist ein Schlüsseltechnologie-Enabler für die Realisierung von kleinen, zuverlässigen und hohen Leistungen Leiterplatten Layouts in den heutigen elektronischen Anwendungen.

Wie man in PAD über macht Leiterplatten ?

Generieren via in PAD Leiterplatten führt auch ein sehr verfeinertes Verfahren der elektrischen Verbindung und Festverbindung ein. Zuerst müssen Sie Ihr Design in Ihrem Leiterplatten Layout-Paket, so dass es weiß, wo auf Ihrem Board Sie Vias haben möchten, die Art von Vias, die Sie verwenden möchten und wie groß sie sein sollten Leiterplatten Hersteller, was Sie gerne haben). Stellen Sie sicher, dass Sie über in PAD haben, wo sie angeschlossen werden. Danach wählen Sie die Lochgröße und das Endfinish entsprechend der Stromtragfähigkeit und dem Signalbedarf aus. Die Leiterplatten wird an der Stelle gebohrt, an der die Vias gewünscht sind, und die Löcher werden mit leitfähigem Material (normalerweise Kupfer) beschichtet, um alle Schichten zu verbinden. Konstruktionsregeln wie Abstand und Ringe müssen befolgt werden, um Kurzschlüsse oder Herstellungsprobleme zu verhindern. Schließlich validieren Sie mittels Funktionalität durch Test und Inspektion die gewünschten Konstruktionsanforderungen und Leistung.

Was ist der IPC-Standard für Via in PAD Leiterplatten ?

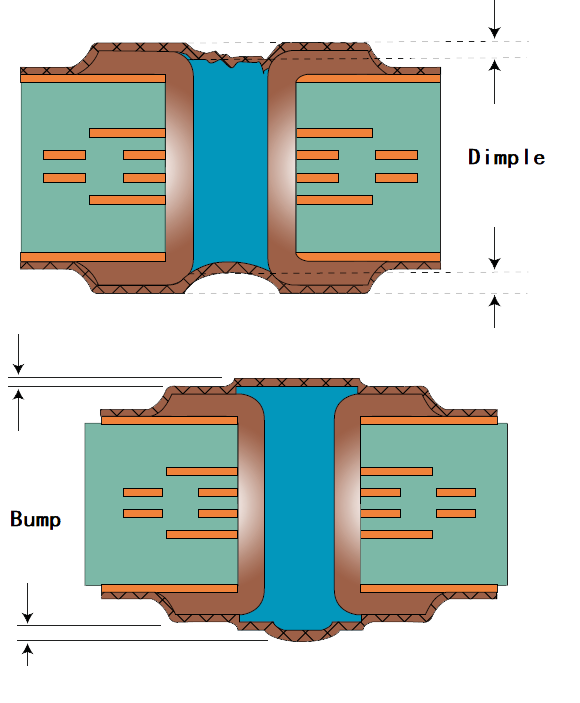

| Artikel | Klasse I | Klasse II | Klasse III |

| Abdeckte Kupferdicke (um) | AABUS | 5 | 12 |

| Dimple max (um) | AABUS | 127 | 76 |

| Stoß max (um) | AABUS | 50 | 50 |

Die IPC-Standards, die für via in pad in gelten Leiterplattendesign IPC-6012 und IPC-4671. IPC-6012 beschreibt die Qualifikations- und Leistungsanforderungen für starre Druckplatten, gibt Leitlinien in den Bereichen Via Design, Auswahl des Bodenmusters und Richtlinien für Fertigungstoleranzen, um sicherzustellen, dass eine hohe Zuverlässigkeit im Produkt erhalten wird. Im Gegensatz dazu befasst sich IPC-4671 mit den Leistungsanforderungen an gedruckte Kartenlaminate, die für die mechanische Stabilität und Funktionalität der Löcher (Vias) von entscheidender Bedeutung sind. Zusammen bieten diese beiden Standards eine vollständige Dokumentabdeckung, um sicherzustellen, dass erfolgreiche Vias in Pad PCBs basierend auf branchenerkannten Qualitäts- und Zuverlässigkeitszielen hergestellt werden.

Zusammenfassend, mit via in PAD Leiterplatten Layout wäre eine gute Möglichkeit, Platz und bessere elektrische Fähigkeit zu nutzen, insbesondere in einigen Hochdichte- und Mehrschichtplatten. Ein solcher Ansatz erforderte jedoch eine angemessene Aufmerksamkeit auf die Lötbarkeit; thermisches Management; und mögliche Zuverlässigkeitsbedenken. Gute Konstruktionspraktiken, wie Lötmaske definierte Pads, richtige Größe Vias, gute Freiheit, sind notwendig, um Probleme wie Lötverwicklung und Hohlräume während der Montage zu vermeiden. Die Zusammenarbeit mit Herstellern und die Einhaltung von Fab-Regeln sind für eine erfolgreiche Durchführung in der PAD-Implementierung unerlässlich. Leiterplatten Integrität und Betriebsfähigkeit.

- 1Was ist Ultra HDI-Leiterplatten ?

- 2HDI-Leiterplatten Marktaussichten 2025: Zukunft Perspektiven, Wachstumsanalyse & Innovationen

- 3Leiterplatte Vollständiger Leitfaden (2024)

- 4Mehrschichtige Rigid- flexible Leiterplatte : Leiterplatten Innovationen in Blind/Begraben über Strukturen

- 5Häufige Ausfallmodi von Rigid flexible leiterplatten

- 6HDI Leiterplattendesign Umfassender Leitfaden: Mastering High Density Interconnect Technology im Jahr 2025

- 7HDI-Leiterplatte Hersteller | Umfassender Leitfaden 2025

- 8Was ist IPC 4761 Typ VII Via in Pad Leiterplatten ?

- 9Wie man wählt a schnelldrehung HDI-Leiterplatte Hersteller?

- 10Transparent Leiterplatten Technologie (2025): Revolutionierendes Elektronikdesign

- Skype-ID: shawnwang2006

- Telefon: +86-755-23724206

- E-Mail-Adresse: sales@efpcb.com

- Schneller Kontakt