HDI Leiterplattendesign Umfassender Leitfaden: Mastering High Density Interconnect Technology im Jahr 2025

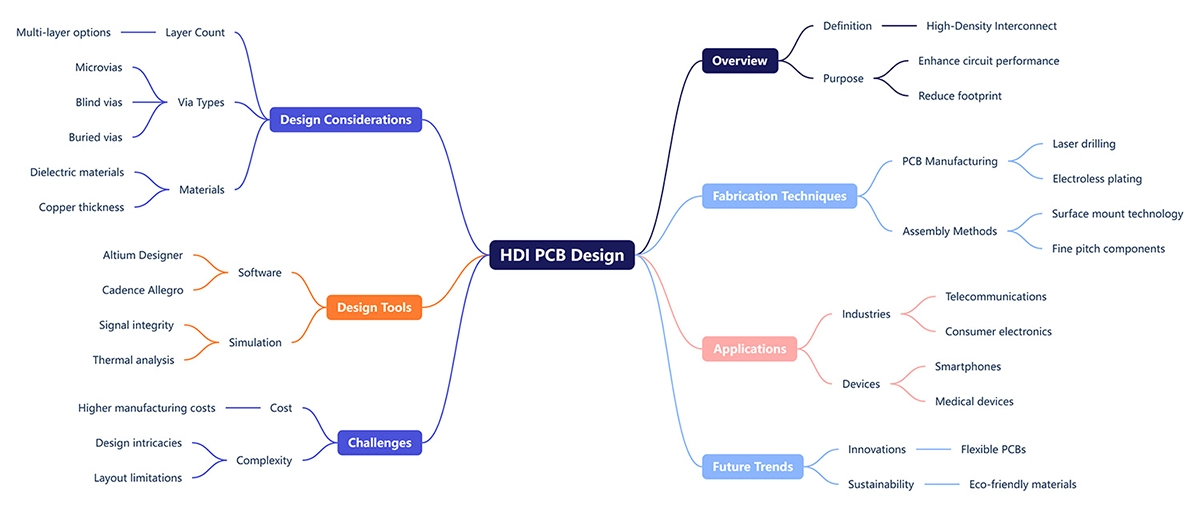

HDI-Leiterplatten (High Density Interconnect) stehen an der Spitze der modernen Elektronikherstellung und ermöglichen die nächste Generation sehr kleiner Formfaktoren und leistungsstarker Geräte. Da sich die Verbraucherelektronik mit zunehmender Funktionalität weiter miniaturisiert, wird HDI Leiterplattendesign ist jetzt eine Anforderung für Ingenieure, die Anwendungen in Smartphones, Tablets, Wearables und High-End-Computersystemen entwerfen.

Laut MarketsandMarkets-Studien ist die weltweite HDI-Leiterplatte Der Markt lag bei 16,2 Milliarden Dollar im Jahr 2024 und wird voraussichtlich bis 2029 auf 24,8 Milliarden Dollar wachsen. Dieser meteorische Anstieg zeigt, wie wichtig HDI ist Leiterplattendesign wird in der fortschrittlichen Elektronik, wie immer schrumpfend Leiterplatten Immobilien und steigende Leistungsanforderungen strecken traditionelle Leiterplatten Technologien bis zum Bruchpunkt.

Verständnis HDI-Leiterplatte Grundlagen der Technologie

HDI Leiterplattendesign Unterscheidet sich stark vom traditionellen Leiterplattendesign mit der Anwendung von Microvias, begraben Vias und blinden Vias für eine höhere Schaltungsdichte. Die Platten haben typischerweise Spurbreiten von 25 Mikrometer und Durchmessern von 50 Mikrometer, im Gegensatz zu herkömmlichen PCBs sind 100 Mikrometer Spuren und 200 Mikrometer Durchmesser selten.

Der Prozess ermöglicht es den Designern, mehr Pferdekraft in engere Fußabdrücke zu packen, indem mehrere Aufbauschichten auf beiden Seiten des Kernsubstrats verwendet werden. Jetzt ist es möglich, eine 20-Schicht zu entwerfen HDI-Leiterplatte mit einer Dicke ähnlich der einer Standard-8-Schicht Leiterplatten Solche Dichteverhöhungen werden durch neue Materialien wie modifizierte Epoxidharze und Polyimidfolien mit hervorragenden elektrischen Eigenschaften und thermischer Stabilität ermöglicht.

Typische definierende Merkmale von HDI Leiterplattendesign umfassen die via-in-pad-Technologie, die es ermöglicht, Komponenten zu bekämpfen, die direkt über Vias platziert werden können, und die sequenzielle Aufbaukonstruktion, bei der verschiedene Schichten inkrementell anstelle gleichzeitig hinzugefügt werden. Diese Fähigkeiten ermöglichen Routing-Dichten weit über 130 Verbindungen pro Quadratzoll im Gegensatz zu 50-70 Verbindungen anderer Typen.

Der Fertigungstechnologieprozess für HDI-Leiterplatten

Produktion von HDI Leiterplattendesign umfasst fortschrittliche sequenzielle Aufbautechnologie, die Kontrolle jedes Details ist unerlässlich. Dieser Flow ist wichtig für Designer, um ihre Layouts für hohe Erträge und Zuverlässigkeit anzupassen.

Substratvorbereitung und Kernverarbeitung

Der Prozess beginnt mit der Herstellung eines Kernmaterials von ausgezeichneter Qualität, das speziell für HDI-Anwendungen entwickelt wurde. Das Substratmaterial ist in der Regel verlustarme Dielektrik, die kontrollierte Dielektrikonstante im Bereich von 3,2 bis 4,5. Bei Verwendung von High-End HDI Leiterplattendesign Substrate einschließlich eingebetteter Komponenten oder Hohlräume können zur Verbesserung der Komponentendichte verwendet werden. Die Hauptverarbeitung besteht aus Bohren, Beschichtungen und Mustern der Grundschichten mit ähnlichen Montageprozeduren fein mit feinen Techniken verwendet in Leiterplatten Mit HDI-Leiterplatte Die Toleranzen müssen jedoch viel strenger sein, mit einer Bohrtoleranz von ±12,5 Mikron und einer Kupferdickentoleranz über die Platte von ±10%. Diese Bereiche gewährleisten die Bildung zuverlässiger Vias in anschließenden Aufbaustufen.

Sequentieller Aufbauschichtbau

Und wenn es darum geht HDI-Leiterplatte Herstellung, das Herz des Prozesses ist die sequenzielle Laminierung Aufbau durch die Zugabe von Schichten, eine für eine. In jeder Aufbauschicht Prepreg-Materialien, die in der Regel 3-5 Millimeter dick sind. Dazu werden sie gelegt und anschließend mit vorgegebener Temperatur und Druck Kupferfolie laminiert.

Die Temperaturen beim Laminieren liegen in der Regel zwischen 130 und 260°C und Drücke zwischen 300 und 400 PSI werden gehalten. Die Aushärtung muss sorgfältig kontrolliert werden, um eine Delamination zu vermeiden und eine gute Verbindung zwischen den Schichten zu erzielen. Vakuum-assistierte Laminierung, die eine leere und gleichmäßige Schichtdicke in modernen HDI-Leiterplatte Herstellung .

Microvia Formationstechnologien

Unter den verschiedenen Schwierigkeiten bei der Herstellung von HDI-Leiterplatte Microvia Bohren ist eines der wichtigsten. Es gibt drei Haupttechnologien, die diesen Prozess steuern: Laserbohren, mechanisches Bohren und Plasmaätzen. Laserbohren mit CO2- oder UV-Lasern ist für 85% der Mikroviaerstellung in HDI verantwortlich Leiterplattendesign Arenen.

Das CO2-Laserbohren in den ultraroten Frequenzen von ca. 10,6 Mikrometer wird verwendet, um organische Stoffe wie die dielektrischen Schichten zu ablieren, die Kupferschichten jedoch unverändert zu lassen. Diese Selektivität erlaubt genaue Tiefen von blinden Vias, die sich durch bestimmte Schichtpaare verbinden. UV-Laser mit 355 Nanometern bieten Leistungsmöglichkeiten unter 75 Mikron.

Die Optimierung des Laserbohrprozesses erfordert eine sorgfältige Parametereinstellung der Impulsenergie, der Wiederholungsrate und des Strahlfokusses. Standardparameter für HDI-Leiterplatte Anwendungen sind Impulsenergien zwischen 0,1-0,5mJ bei Wiederholungsraten von 1-10kHz. Diese Bedingungen werden durch Bildungsraten von 200-500 Löchern pro Sekunde und Genauigkeit der Löchergröße innerhalb von ±5 Mikron realisiert.

Metallisierungs- und Beschichtungsprozesse

Nach der Bildung, HDI Leiterplattendesign Die Herstellung erfordert spezielle Metallisierungstechniken, um stabile elektrische Verbindungen bereitzustellen. Behandlungen wie Permanganatlösungen oder Plasma zur Desmearierung, um das Harz von über Wände zu entfernen und die Kupferhaftung zu verbessern.

Ablagerung der ursprünglichen leitfähigen Schicht, üblicherweise 0,2 bis 0. 5 µm und eine elektrolytische Kupferbeschichtung mit einer Enddicke von 15 bis 25 µm. Die Beschichtung muss auch eine konsistente Verteilung der Dicke zwischen allen Durchmessergrößen und Seitenverhältnissen bieten, die sich in HDI stark unterscheiden Leiterplattendesign verwendet.

Gefüllte Vias – viel oder wenig? Moderne HDI Leiterplattendesign verwendet oft gefüllte Vias mit leitfähigen oder nicht-leitfähigen Materialien. Leitfähige Füllung verwendet Kupferpaste oder hoch silbergefülltes Epoxy, während nicht leitende Füllung spezielle Harze verwendet, die für die weitere Verarbeitung gehabelt werden könnten. Diese Konstruktion ermöglicht eine (VIP) Via-in-Pad-Konstruktion und ein verbessertes Wärmemanagement bei Hochleistungssystemen.

Musterbildung und Ätzung

Im HDI Leiterplattendesign Die Schaltungsmusterbildung erfordert ein hohes Maß an Photolithographiewerkzeug, das feinliniengeometrien erstellen kann. Typischerweise wird Trockenfilmphotoresist mit einer Dicke von 15-40 Mikrometern eingesetzt, abhängig von der erforderlichen Kupferdicke und Leitungsbreite.

Die Auflösungsfähigkeit der Belichtungssysteme sollte 10 Mikrometer oder weniger betragen und die Ausrichtungsgenauigkeit zwischen den Ebenen muss +5 Mikrometer betragen. Prozess des HDI Leiterplattendesign Produktion heute, die Leiterplatten Die Industrie profitiert von Direktbildsystemen, die keine Fotomasken erfordern und zu einer höheren Präzision und einer schnelleren Produktion führen.

Unerwünschtes Kupfer wird beim Ätzen entfernt, während gewünschte Schaltungsmuster geschützt sind. Alkalische Ätzer, in der Regel Kupferchlorid oder Eisenchlorid, werden bei kontrollierter Temperatur, Konzentration und Sprühdruck eingesetzt. Die Ätzraten müssen optimal angepasst werden, um die Gleichmäßigkeit der Linienbreitenregelung zu gewährleisten und den Unterschnitt auf ein Minimum zu halten.

Oberflächenveredelung und Endbearbeitung

HDI-Leiterplatte Herstellung endet mit Oberflächenbehandlungen, die dazu dienen, das freigestellte Kupfer zu schützen und das Löten zu ermöglichen. Häufige Oberflächen sind Electroless Nickel Immersion Gold (ENIG), Immersion Silver und Organic Solderability Preservative (OSP).

Das Gold CSC erreicht eine Dicke zwischen 0,05 und 0,2 µm auf ca. 3-6 µm Nickel durch ENIG, das am besten geeignete Veredelungsverfahren für Feinsteigungsanwendungen. Diese Blei-Oberfläche hat eine gute Lötbarkeit und Drahtbindbarkeit und ist widerstandsfähig gegen Lagerung. Der Prozess beinhaltet die Aufrechterhaltung der Badechemie und der Temperatur mit feiner Kontrolle, um schwarze Pad-Defekte zu beseitigen, die die Gelenkzuverlässigkeit reduzieren können.

Nach der endgültigen Verarbeitung werden die Einheiten dann elektrisch mit fliegender Sonde oder Nägelbettarmaturen geprüft, die die sehr dichte Prüfpunktzahl erreichen können, die typisch für HDI-Leiterplatte Versus Paket Design Stil. Das AOI-System muss die maximalen und minimalen Abmessungen sowie Mängel bestätigen, die einen Ausfall in der Montage verursachen können.

Qualitätskontrolle und Prüfprotokolle

Hochdichte Interconnector Leiterplatten Layout Produktion erfordert eine strenge Qualitätskontrolle im Produktionsprozess. Die statistische Prozesssteuerung dient zur Überwachung kritischer Parameter wie Größenverteilung, Kupferdicke und -gleichmäßigkeit sowie Abmessungen. Typische Regelgrenzen erlauben keine Abweichung des Durchmessers von mehr als ± 10 % vom Nenngewicht oder das Kupfergewicht beträgt ± 15 %.

HDI-Leiterplatte Zuverlässigkeitsprüfprotokolle sind thermischer Zyklus, Vibrationsprüfung und beschleunigtes Altern mit kontrollierter Temperatur und Feuchtigkeit. Diese Tests bestätigen, dass der sequenzielle Aufbauprozess die Belastungen, die in Endanwendungen erfahren werden, tolerieren kann.

Zukünftige Trends und Innovationen

Das HDI-Design entwickelt sich weiter mit Innovationen wie Embedded-Komponententechnologie, 3D-Druck von leitfähigen Spuren und fortschrittlichen Materialien mit überlegenen thermischen und elektrischen Eigenschaften. Diese Entwicklungen deuten darauf hin, dass die Miniaturisierung und Funktionalisierung der Elektronik neue Höhen erreichen kann.

Laut Industriestudie wird es künstliche Intelligenz in der nächsten Generation HDI-Leiterplatte zur automatisierten Routing-Optimierung und prädiktiven Qualitätskontrolle. Diese Fortschritte werden die Fertigungseffizienz weiter steigern und gleichzeitig neue Niveaus an Schaltungsverpackungsdichte und -leistung einführen.

Häufig gestellte Fragen zu HDI Leiterplattendesign

Was ist die kleinste VIA, die in HDI erreicht werden kann Leiterplattendesign Heute?

Der kleinste akzeptable Gesamtdurchmesser beträgt derzeit etwa 50 (und in einigen spezialisierten Verfahren 25) Mikrometer. Allerdings 75-100 Mikrometer Vias sind typischer in einer Produktion HDI Leiterplattendesign aus Zuverlässigkeit- und Ertragsgründen.

Was ist ein Maximum in HDI Leiterplattendesign in Bezug auf Aufbauschichten?

Heute ist HDI Leiterplattendesign unterstützt den Aufbau von bis zu 6 Schichten auf jeder Seite des Kerns, was zu Boards mit insgesamt 20+ Schichten führt. Allerdings werden in den meisten kommerziellen Anwendungen 2-4 Aufbauschichten pro Seite eingesetzt, um Kosten und Komplexität zu beeinträchtigen.

Was macht HDI Leiterplattendesign Kosten im Vergleich zu einer regulären Leiterplatten ?

HDI Leiterplattendesign ususally ist etwa 2-5 mal höher als ähnliche konventionelle Leiterplatten Boards als den Erwerb spezifischer Rohstoffe und den Einsatz spezifischer Ausrüstung. Aber die zusätzlichen Kosten werden oft gegen niedrigere Montagekosten und bessere Produktleistung gehandelt.

Was sind die Konstruktionsregeln für HDI zu befolgen Leiterplattendesign Ist das erfolgreich?

Die wichtigsten Konstruktionsregeln sind eine Mindestspurbreite von 50 μm, ein Mindestabstand von 100 μm und die Vermeidung akuter Winkel in den Filmkreislinien. Signalintegrität – Ebenso wichtig ist die Stapel- und Impedanzsteuerung.

Wie wird die thermische Konstruktion von HDI beeinflusst Leiterplattendesign ?

HDI-Leiterplatte Designs können beim thermischen Management helfen, indem höhere Konzentrationen an Kupfer sowie thermische Vias verwendet werden. Aber das Vorhandensein dünner dielektrischer Schichten und hoher Komponentendichte kann auch zu thermischen Problemen führen und sollte bei der thermischen Modellierung und Optimierung von Layouts berücksichtigt werden.

Gut beherrschter HDI Leiterplattendesign Fertigungstechnik ist heute ein sehr wichtiger Wettbewerbsvorteil in der Elektronikindustrie. Da Geräte immer mehr Funktionen in kleineren Produkten erfordern, sind Kenntnisse dieser fortschrittlichen Fertigungsschritte von entscheidender Bedeutung für eine erfolgreiche Produktentwicklung und Marktführerschaft.

Nicht mehr

- 1Was ist Ultra HDI-Leiterplatten ?

- 2Leiterplatte Vollständiger Leitfaden (2024)

- 3HDI-Leiterplatten Marktaussichten 2025: Zukunft Perspektiven, Wachstumsanalyse & Innovationen

- 4Mehrschichtige Rigid- flexible Leiterplatte : Leiterplatten Innovationen in Blind/Begraben über Strukturen

- 5HDI Leiterplattendesign Umfassender Leitfaden: Mastering High Density Interconnect Technology im Jahr 2025

- 6Häufige Ausfallmodi von Rigid flexible leiterplatten

- 7HDI-Leiterplatte Hersteller | Umfassender Leitfaden 2025

- 8Was ist IPC 4761 Typ VII Via in Pad Leiterplatten ?

- 9Wie man wählt a schnelldrehung HDI-Leiterplatte Hersteller?

- 10Transparent Leiterplatten Technologie (2025): Revolutionierendes Elektronikdesign

- Skype-ID: shawnwang2006

- Telefon: +86-755-23724206

- E-Mail-Adresse: sales@efpcb.com

- Schneller Kontakt