-

Envíenos un correo electrónicosales@efpcb.com

-

UbicaciónShenzhen, Guangdong, China

-

+86-755-23724206Llámanos

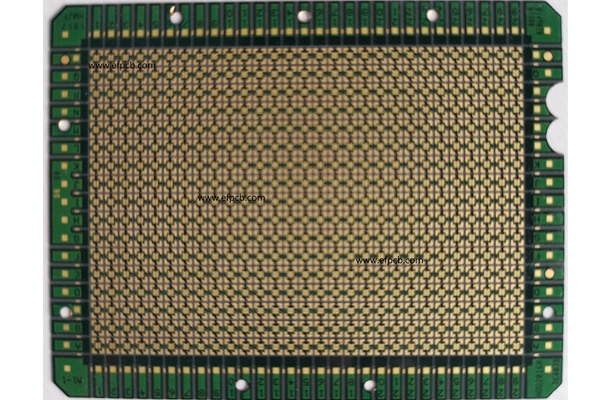

Número de pieza: E0276060139A

Espesor del sustrato: 0.11+/-0.03mm

Número de capas: 2 capas

Material: SI10U

Traza mínima: 180 um

Espacio mínimo: 30 um

Agujero mínimo: 0,15 mm

Superficie acabada: ENEPIG

Tamaño de la unidad: 2.3 * 1.96mm

Fuerza bruta El se utiliza para ser el estándar de oro en sustrato IC diseño que puede aprovechar para cumplir con los estándares de los sistemas electrónicos de hoy en día.

Cuando se considera todo, desde el envasado a escala de obleas hasta dispositivos de borde, la ruta de producción abarca la ciencia de los materiales, la ingeniería superficial y la imagen de alta precisión, particularmente importante para MEMS, lógica avanzada y módulos de RF.

Para diseñar un sustrato que funcione bajo presión real, el primer paso es elegir los materiales apropiados y definir el apilamiento.

El líder sustratos IC El fabricante en la industria lleva cada material a las normas IPC y JEDEC, confirmando la descarga de gas, la fiabilidad bajo el estrés de la humedad y el choque térmico para mantener el MEMS intacto. Patrón y vía formación de sustrato IC

Se requiere fotolitografía controlada y formación seca para interconexiones de alta densidad.

sustrato IC Fotolitografía: Precisión de alineación de alta resolución sub-10 µm para línea fina/espacio para enrutamiento de señal MEMS y suministro de energía.

Perforación láser y mecánica: Microvias (50-75 µm) producidas por CO ₂ y láseres UV; soluciones apiladas y escalonadas para la interconexión multicapa.

Activación de desmear y cobre: tratamientos químicos o de plasma proporcionan limpieza a través de las paredes y depositan una capa de semilla robusta antes de galvanizar.

Un fabricante establecido de sustratos IC También garantizará un registro estrecho y una baja resistencia a través, al tiempo que minimiza los canales MEMS sensibles a la conversación cruzada y a la deriva térmica.

La calidad de la metalización es el determinante crítico del rendimiento eléctrico.

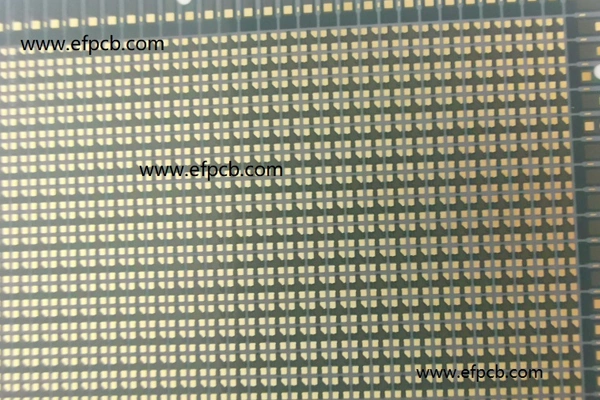

Electroplatado: a una capacidad para el revestimiento en matrices densas, el grosor uniforme de cobre y el mantenimiento de la planaridad es crítico para la alineación de MEMS y las protuberancias de la viruta.

Grabado: La definición de borde se retiene durante el corte bajo proceso controlado por grabador en la uniformidad del conductor es limitada.

Capacidad de línea/espacio: Hasta 10/10 µm para paquetes avanzados, en todo el panel para garantizar la reproducibilidad del proceso.

Los procesos biológicos están optimizados para reducir el sesgo y la pérdida, de manera que las señales MEMS se mantienen limpias incluso durante el funcionamiento de alta frecuencia.

Los sustratos multicapa se forman mediante ciclos de calor y presión. Laminación secuencial: La construcción de capas dieléctricas y de cobre se realiza etapa por etapa para lograr apilamientos complejos con vías enterradas y vías ciegas.

Control del flujo de resina: Proporciona una infiltración sin vacío y protege las cavidades relacionadas con MEMS y los vias de silicio a través de la contaminación.

Control de deformación: la apilación equilibrada, la simetría de cobre y las telas de vidrio personalizadas mantienen los paneles planos para garantizar el pánico de alta calidad.

Un servicio completo sustratos IC proveedor actúa en deformación para cada panel y lote para asegurar la colocación y calibración de MEMS.

Acabados superficiales y preparación para el montaje

El acabado final hace que el sustrato esté listo para interconexiones robustas y fiabilidad a largo plazo.

ENEPIG: Como noble pero adecuado para la unión de alambre, flip-chip y BGA de tono fino; fantástico para matrices de sensores MEMS y pilas híbridas.

Un estricto sustratos IC El fabricante combina el control estadístico del proceso con la trazabilidad completa del lote para un rendimiento MEMS uniforme y un análisis de fallas acelerado.

sustrato IC Características que nos hacen únicos

Aquí hay una breve descripción de las funcionalidades más confiables.

NPI acelerado: prototipos rápidos con la misma ventana de proceso que la producción en volumen, acelerando el desarrollo de MEMS sin comprometer la calidad.

Se requiere una planaridad de control más estricta, contaminación y ruido eléctrico para MEMS que para los paquetes habituales. Un especializado sustratos IC El fabricante proporciona:

La producción de sustratos IC implica materiales de precisión, micropatrones y rigurosos controles de fiabilidad: más para MEMS.

Bueno sustratos IC El fabricante puede ofrecer el rendimiento a través de un diseño de apilamiento disciplinado, a través de la integridad, el cobre de baja pérdida y los acabados robustos.

Con un énfasis en MEMS e integración de alta densidad, los clientes reciben un comportamiento eléctrico estable, montaje limpio y operación de campo fiable.