IC基板設計在降噪與信號完整性中的關鍵作用

關鍵詞:IC載板

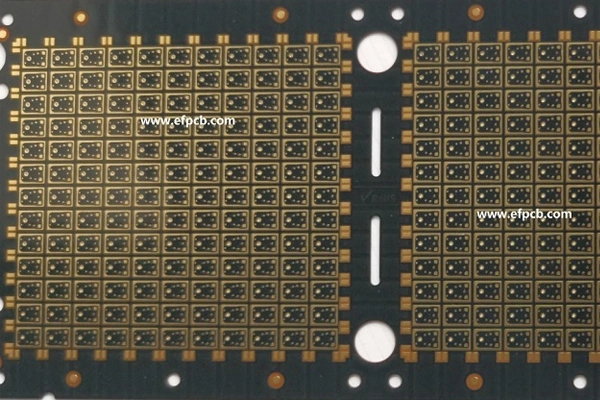

在速度和效率至關重要的快速發展的電子設備領域中,保持信號完整性並降低噪聲已成為關鍵挑戰。積體電路構成了現代電子系統的骨幹,其性能在很大程度上依賴於IC載板的複雜設計。在本篇部落格中,我們將深入探討IC載板設計在確保最佳信號完整性和最小化噪聲方面的重要性,探索這個基本方面如何在電子設備的無縫運作中發揮關鍵作用。

信號完整性

信號完整性是指信號在電路中傳輸時保持其原始品質的能力。在積體電路領域,這是一個多方面的問題,因為信號在日益微型化的晶片上穿行複雜的路徑。任何與預期信號的偏差都可能導致資料損壞、性能下降,甚至系統故障。IC載板雖然常被忽視但至關重要,它在保持信號完整性方面扮演著核心角色。

材料選擇:信號完整性的基礎

基板材質的選擇是保持信號完整性的第一道防線。具有優異電氣性能的高品質材料,例如低介電常數和低損耗角正切,是必不可少的。這些特性有助於信號的平穩傳播,減少信號失真或衰減的可能性。常見的基板材料包括FR-4、陶瓷和專用的高頻層壓板,每種材料都針對應用的特定需求而量身定制。

走線佈局與阻抗控制:精確性至關重要

走線佈局指的是IC載板上導電路徑的佈局。這些走線佈局的精確度和細心程度直接影響信號完整性。沿著這些路徑保持受控的阻抗對於防止信號反射和確保信號保真度至關重要。先進的設計技術,例如差動信號傳輸和阻抗匹配,對於最小化信號失真和串擾變得不可或缺。

在IC載板設計中減輕噪聲

噪聲,一種不需要的電氣干擾,對電子設備的可靠性構成持續威脅。在複雜的IC設計世界中,有效的降噪策略對於實現最佳性能是不可或缺的。

接地與電源分佈:噪聲減輕的支柱

設計良好的接地和電源分佈系統是降低噪聲的基礎。正確的接地可以最小化接地迴路,並為IC上的所有元件確保穩定的參考電位。同時,高效的電源分佈網絡保證了整個晶片的均勻供電,防止可能將噪聲引入系統的電壓波動。

去耦電容器:抵禦電壓波動的守護者

去耦電容器充當抵禦電壓波動的守護者,穩定電源供應並減輕高頻噪聲。這些電容器策略性地放置在IC載板上,根據需要儲存和釋放能量,為敏感元件提供穩定的電源。它們的正確選擇和佈局對於維持一個乾淨且無噪聲的電源傳輸網絡至關重要。

屏蔽技術:防禦外部干擾

在無線連接和擁擠的電磁頻譜時代,外部干擾是一個持續關注的問題。將屏蔽技術納入IC載板設計中變得至關重要,以保護敏感信號免受不必要的電磁輻射。屏蔽層或接地層可以充當屏障,防止外部噪聲滲入電路。

設計與模擬的協同作用:良性循環

IC載板設計並非一蹴而就,而是一個高度依賴模擬與分析的迭代過程。先進的模擬工具使設計師能夠預測並理解信號與雜訊在不同情境下的行為。透過根據模擬結果反覆優化設計,工程師可以微調IC載板,以實現最佳的信號完整性與雜訊抑制。

高頻考量

高頻應用的普及,尤其是5G通訊的到來,為IC載板設計帶來了獨特的挑戰。隨著頻率飆升,信號波長縮短,使得佈局與阻抗控制變得更加關鍵。選擇具有增強高頻特性的載板材料,以滿足這些應用的需求,已變得至關重要。

微型化與整合

對更小、更整合裝置的不懈追求,為IC載板設計帶來了雙重挑戰。一方面,微型化要求佈線與載板佈局達到更高的精密度。另一方面,元件間的緊密排列增加了干擾與串音的風險。載板設計的創新必須應對這些相互衝突的需求,在尺寸與性能之間取得微妙的平衡。

先進封裝技術

封裝技術的演進,例如系統級封裝(SiP)與3D堆疊,為IC載板設計引入了新的維度。這些封裝創新實現了元件更緊密的整合,但也需要重新評估信號路徑、電源分配與熱管理。未來的載板設計必須適應這些不斷變化的封裝範式,確保兼容性與最佳性能。

跨學科協作

現代電子系統的複雜性需要跨多個工程學科的協作方法。電氣工程師、材料科學家與封裝專家必須協同工作,以應對信號完整性與雜訊抑制帶來的多面向挑戰。跨學科協作不僅豐富了設計過程,也催生了推動行業前進的創新。在這個動態環境中,工程師與研究人員必須持續突破載板設計的界限,善用材料、模擬工具與封裝技術的進步。設計、模擬與優化的良性循環將持續下去,引導IC載板的演進,以滿足未來電子裝置的需求。

結論

在對更快、更高效電子裝置的不懈追求中,IC載板設計的重要性怎麼強調都不為過。它是將信號與元件構成的複雜網絡緊密結合的關鍵,確保了無縫通訊與最佳性能。隨著技術不斷進步,維持信號完整性和降低雜訊的挑戰將持續存在,這使得IC載板設計的角色變得更加關鍵。對載板設計採取一絲不苟且深思熟慮的方法,不僅是設計過程中的一個必要步驟,更是釋放現代電子系統全部潛力的基本要求。現代電子系統建構於積體電路之上,而IC載板的複雜架構對IC的功能表現有著重大影響。

高溫印刷電路板建模與模擬

- Skype: shawnwang2006

- 電話: +86-755-23724206

- 電子郵件: sales@efpcb.com

- 快速聯系