Znaczenie płyt obciążeniowych w testowaniu półprzewodników

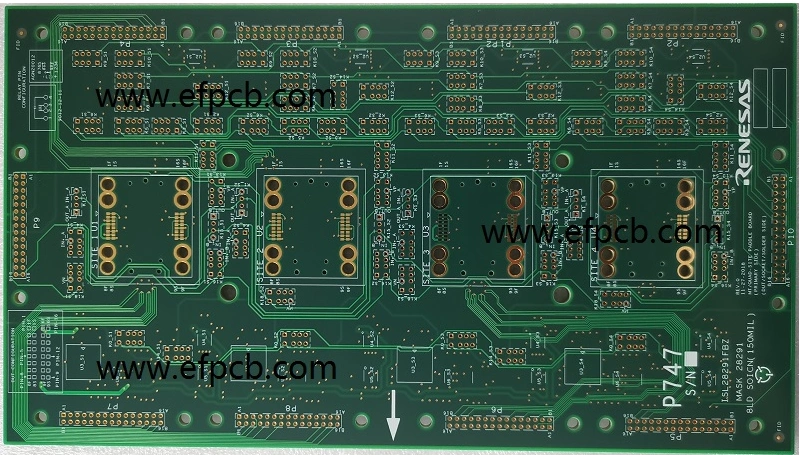

Płyta Obciążeniowa (LB) to specjalnie zaprojektowany obwód drukowany (PCB), który służy jako mechaniczne i elektryczne połączenie między analizatorem (ATE) a testowanym urządzeniem. Płyty Obciążeniowe mają określone wymiary fizyczne i muszą precyzyjnie pasować wewnątrz analizatora. Zazwyczaj płyta obciążeniowa składa się z dwóch punktów interfejsu: Jeden interfejs skierowany jest w stronę jednostki sterującej analizatora. Hander to zautomatyzowana jednostka pick-and-place, która usuwa DUT z tacy i umieszcza go w gnieździe. Drugi punkt interfejsu skierowany jest w dół, w stronę pinów "pogo" analizatora. Są to porty wejścia/wyjścia analizatora, które łączą go elektrycznie z DUT.

Właściwości Płyty Obciążeniowej

Dobrze skonstruowana LB jest elektrycznie niewykrywalna i nie wprowadza zniekształceń ani opóźnień do sygnałów DUT. Płyta Obciążeniowa powinna być zdolna do obsługi wszystkich testów wykonywanych na analizatorze oraz być wystarczająco elastyczna, aby uwzględnić przyszłe testy (na przykład poprzez rozszerzenie rozwiązania testowego o testowanie równoległe w czterech kanałach).

Wielu inżynierów testowych dąży do umieszczenia wszystkich elementów aktywnych poza LB, pozostawiając jedynie elementy pasywne niezbędne do umożliwienia funkcjonalności ASIC. Tendencja do upraszczania Płyty Obciążeniowej wynika z chęci zmniejszenia prawdopodobieństwa awarii na etapie produkcji, co mogłoby spowodować zatrzymanie linii produkcyjnej. Czas potrzebny na naprawę problemu pojawia się, gdy Płyta Obciążeniowa jest bardziej złożona.

Różne analizatory (ATE) wymagają różnych rozmiarów LB. Jednakże wszystkie Płyty Obciążeniowe składają się z podobnych elementów:

- Gniazdo dla ASIC DUT z podkładkami interfejsowymi dla analizatora

- Wzmocnienie zwiększające wytrzymałość mechaniczną.

- Kilka komponentów w zależności od potrzeb DUT (R, C, itp.)

- Złącza dla etapu badania (Probe)

W określonych warunkach, oprócz bycia płytą interfejsową, LB może również zawierać wbudowane możliwości testowania. Gdy sam analizator nie może obsłużyć konkretnego zadania testowego, może ono być przeprowadzone bezpośrednio na LB.

Zasady konfiguracji płyty obciążeniowej

Płyta Obciążeniowa może być zaprojektowana przez prawie każdego inżyniera układów lub PCB; jedynym wymaganiem jest podstawowe zrozumienie testów i koncepcji Płyty Obciążeniowej. LB jest często wykonana z materiału RF4 i jest niezwykle gruba, z co najmniej 20 warstwami.

Zagadnienia projektowe Płyty Obciążeniowej są porównywalne z tymi dla innych PCB. Rozmieszczenie zasilania, prowadzenie sygnałów zegarowych, trasowanie szybkich transmisji, integralność sygnału, długość ścieżek — te zasady projektowe również tu obowiązują. W pewnych warunkach wskazane jest przeprowadzenie symulacji elektrycznej, szczególnie w celu zapewnienia wydajności sygnałów RF.

Po zakończeniu projektu układu, kolejnym krokiem jest wytworzenie/powstanie płytki oraz zmontowanie jej z różnymi elementami pasywnymi lub aktywnymi i gniazdami.

Płyta obciążeniowa jest kluczowym elementem systemu testowania ASIC. Stwórz solidny, ale prosty projekt, aby zapewnić mniej problemów produkcyjnych; jeśli to możliwe, zachowaj jedną płytę jako zapasową.

Chociaż zawsze istniała potrzeba weryfikacji płyty obciążeniowej, przejście na technologię montażu powierzchniowego (SMT) zwiększyło to zapotrzebowanie. Gniazda testowe układów scalonych ze sprężynowymi sondami wprowadziły duży kontakt elektromechaniczny do zespołu złącza testowego, co może potencjalnie negatywnie wpłynąć na dokładność i integralność testów obudowy układu scalonego.

Płyta obciążeniowa, znana również jako jednostka interfejsu testowego lub płyta wykonawcza, łączy testowany układ scalony z głowicą testową analizatora parametrycznego lub zautomatyzowanego sprzętu testowego (ATE). Płyta obciążeniowa jest często wykonana z gniazda testowego lub kontaktora, który utrzymuje układ scalony i łączy się z obwodem drukowanym (PCB), zwanym również płytą DUT lub ATE, która łączy się z głowicą testową ATE.

Najlepiej, gdy płytka testowa służy jako zasadniczo proste połączenie mechaniczne i elektryczne między układem scalonym a ATE. Umożliwia to precyzyjną i niezawodną ocenę integralności i wydajności obwodów układu scalonego.

Przetestowanie płytki testowej pod kątem ciągłości przed użyciem jej do badania układu scalonego może zaoszczędzić czas i pieniądze.

Weryfikacja Płytki Testowej

Istnieją trzy główne podejścia do weryfikacji działania płytki testowej. Najbardziej podstawową metodą jest ręczna weryfikacja. W tego rodzaju teście omomierz szuka zwarć lub przerw w połączeniach między gniazdem testowym a układem scalonym oraz między płytką PCB a ATE.

Chociaż ta metoda testowania ma ograniczenia, może być opłacalna dla urządzeń o małej liczbie wyprowadzeń, zazwyczaj poniżej 50. Jednakże to podejście testowe nie jest ani praktyczne, ani opłacalne dla złożonych systemów z wieloma połączeniami.

Na drugim końcu spektrum można użyć tego samego, wartego miliony dolarów ATE, które służy do testowania urządzeń, aby zatwierdzić płytkę testową. Ta metoda jest kosztowna, nieefektywna i może marnować kluczowe zasoby testowe. Nawet jeśli ATE nie jest w pełni wykorzystywane do testowania układów scalonych, dodatkowe oprogramowanie i różne modyfikacje mogą być potrzebne do wsparcia weryfikacji płytki testowej.

Trzecia opcja wykorzystuje dedykowany system testowania płytek testowych. Zazwyczaj ma on niższy koszt niż ATE oraz szybszy i bardziej niezawodny proces testowania niż testowanie ręczne.

Dedykowany system testowy, podobnie jak ręczna lub ATE weryfikacja płytki testowej, monitoruje rezystancję i prądy upływu, aby zapewnić brak przerw lub zwarć w sprzęcie interfejsowym. System dedykowany monitoruje rezystancję obwodu, prądy upływu i pojemność, porównując je ze znanymi wartościami.

System testowy ocenia również działanie różnych diod prostowniczych, diod Zenera i kombinacji szyn. Ponadto, opcje systemu mogą wspierać testowanie przekaźników i komponentów wysokonapięciowych, które mogą być częścią sprzętu płytki testowej.

Często poruszaną kwestią jest to, czy impedancja powinna być oceniana jako część testu płytki testowej. Impedancja i opóźnienia propagacji są wynikiem procesu projektowania płytki DUT, który obejmuje testowanie przy użyciu reflektometrów w dziedzinie czasu.

Kluczową cechą dedykowanego systemu testowania płytek testowych jest jego elastyczność w symulacji różnych głowic testowych. Powinien zapewniać szeroki zakres emulatorów głowic testowych, aby dokładnie sprawdzać wydajność płytek testowych dla różnych typów ATE.

Elastyczność i adaptacyjność systemu testowego są ściśle powiązane z tym, jak szybko i efektywnie jeden emulator głowicy testowej może zostać zastąpiony innym. Dedykowany system testowy jest umieszczany w serwisie producenta, a nie na hali testowej, więc narzędzia i inny sprzęt diagnostyczny są łatwo dostępne, co oszczędza jeszcze więcej czasu.

Dedykowany system testowania płytek testowych zapewnia również kilka możliwości symulacji. Test można umieścić w kontaktorze lub gnieździe testowym, aby przeprowadzić punktowy test rezystancji między stykami gniazda a stykami głowicy testowej na PCB. To podejście gwarantuje dobre zakończenie połączenia gniazdo-PCB, co jest szczególnie krytyczne, gdy gniazdo jest przylutowane do PCB.

Alternatywnie, zainstaluj zwierane urządzenie w gnieździe. To podejście wykorzystuje test rezystancji drogi powrotnej do weryfikacji ciągłości. Wreszcie, niestandardowy emulator urządzenia, często dostarczany przez producenta układu scalonego, może sprawdzać ciągłość za pomocą testu rezystancji w układzie łańcuchowym (daisy-chain).

Dedykowany system testowania płytek testowych jest również przydatny do oceny i wymiany styków sprężynowych w gniazdach SMT. Interfejsy SMT mogą być testowane za pomocą przyrządu do pomiaru rezystancji styku przed montażem na płytce testowej. Przyrząd umożliwia również diagnostykę offline i wymianę wadliwych styków sprężynowych.

Gdy projektanci półprzewodników kontynuują integrację układów scalonych, które mieszczą więcej podzespołów w mniejszych przestrzeniach, z większą liczbą wyprowadzeń i węższymi odstępami, potwierdzanie wydajności obudowy układu scalonego stanie się coraz trudniejsze. Weryfikacja płytki obciążeniowej przed użyciem jej do testowania układów scalonych może zaoszczędzić zarówno czas, jak i pieniądze. Wykorzystanie dedykowanego sprzętu testowego do płytek obciążeniowych pozwala również sprawdzić wydajność różnych projektów płytek obciążeniowych w szerszym zakresie pomiarowym. Ostatecznie umożliwi to przechowywanie i porównywanie danych pomiarowych w celu opracowania harmonogramów konserwacji i wymiany płytek.

- 1Elastyczne obwody drukowane

- 2Laminat pokryty miedzią (surowiec PCB CCL)

- 3Obwody drukowane o dużej gęstości połączeń (High Density Interconnect - HDI)

- 4Jak stworzyć mSAP PCB ?

- 5Technologia produkcji elastycznych płytek PCB (giętkich obwodów drukowanych: rozwój technologii, główne użyte materiały, proces produkcyjny, rodzaje, zastosowania, zalety i wady)

- 6High Quality PCB osiągnięcia

- 7obwody drukowane Kompletny przewodnik (2024)

- 8Czym jest Ultra płytka drukowana HDI ?

- 9Przyszłość Firmy

- 10Czym jest IPC 4761 Typ VII Via w Pad PCB ?

- Skype ID: shawnwang2006

- Telefonu: +86-755-23724206

- Poczta e-mail: sales@efpcb.com

- Szybki kontakt