-

Napisz do nassales@efpcb.com

-

Lokalizacja firmyShenzhen, Guangdong, Chiny

-

+86-755-23724206Zadzwoń do nas

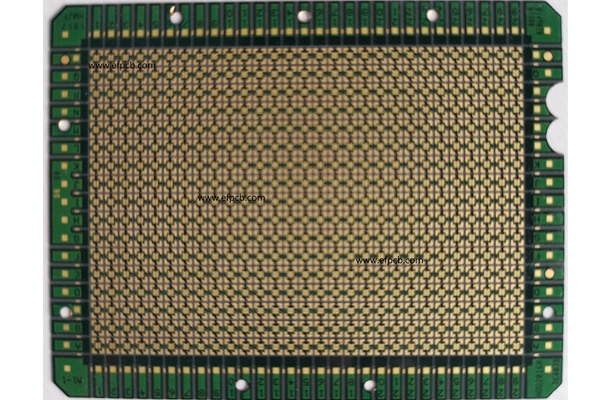

Nr części: E0276060139A

Grubość podłoża: 0,11 +/- 0,03 mm

Liczba warstw: 2 warstwy

Materiał: SI10U

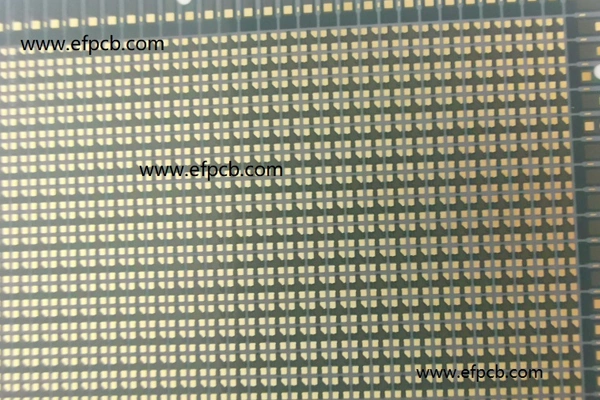

Minimalny ślad: 180 um

Minimalna przestrzeń: 30 um

Minimalny otwór: 0,15 mm

Powierzchnia wykończona: ENEPIG

Rozmiar jednostki: 2,3 * 1,96 mm

Brute force jest używany jako złoty standard w podłoże IC projekt, który można wykorzystać do spełnienia standardów dzisiejszych systemów elektronicznych.

Jeśli wziąć pod uwagę wszystko, od opakowania na skalę płytek po urządzenia krawędziowe, droga produkcyjna obejmuje naukę o materiałach, inżynierię powierzchniową i wysoko precyzyjne obrazowanie - szczególnie ważne dla modułów MEMS, zaawansowanej logiki i modułów RF.

Aby zaprojektować podłoże, które będzie działało pod ciśnieniem w świecie rzeczywistym, pierwszym krokiem jest wybór odpowiednich materiałów i definiowanie stosu.

Główny podłoża IC producent w przemyśle przynosi każdy materiał do standardów IPC i JEDEC, potwierdzając degazowanie, niezawodność pod naprężeniem wilgotności i wstrząs termiczny, aby utrzymać MEMS w stanie nienaruszonym. Wzorowanie i poprzez tworzenie podłoże IC

Do połączeń o wysokiej gęstości wymagana jest kontrolowana fotolitografia i sucha formacja.

podłoże IC Fotolitografia: Dokładność wyrównania o wysokiej rozdzielczości poniżej 10 µm dla drobnej linii / przestrzeni do routingu sygnału MEMS i dostawy mocy.

Wiertanie laserowe i mechaniczne: Microvias (50–75 µm) produkowane przez CO ₂ lasery UV; rozwiązania stosowane i stopniowe do połączeń wielowarstwowych.

Aktywacja desmear i miedzi: Obróbki plazmowe lub chemiczne zapewniają czystość przez ściany i osadzają solidną warstwę nasion przed galvanizacją.

Założony producent podłoża IC zapewni również ścisłą rejestrację i niską odporność, minimalizując jednocześnie kanały MEMS wrażliwe na przemówienie i dryf termiczny.

Jakość metalizacji jest krytycznym determinantem wydajności elektrycznej.

Galwanizacja: przy zdolności do powlekania na gęstych tablicach jednolita grubość miedzi i utrzymywanie płaskości jest kluczowe dla wyrównania MEMS i zwrotu szczupów.

Etrowanie: definicja krawędzi jest zachowana podczas etrowania kontrolowanego procesu podcięcia jednorodności przewodnika jest ograniczona.

Zdolność linii/przestrzeni: do 10/10 µm w przypadku zaawansowanych pakietów, na całym panelu, aby zapewnić powtarzalność procesu.

Procesy biologiczne są zoptymalizowane w celu zmniejszenia odchyleń i strat, dzięki czemu sygnały MEMS są utrzymywane w czystości nawet podczas pracy o wysokiej częstotliwości.

Podłoża wielowarstwowe są tworzone przez cykle ciepła i ciśnienia. Laminacja sekwencyjna: Budowanie warstw dielektrycznych i miedzianych jest wykonywane etap po etapie, aby osiągnąć złożone stosowania z zakopane vias i ślepe vias.

Kontrola przepływu żywicy: Zapewnia bezproblemową infiltrację i chroni przed zanieczyszczeniami jamy związane z MEMS i viami krzemowymi.

Kontrola warpu: Zrównoważone układanie, symetria miedzi i indywidualne szklane tkaniny utrzymują panele płaskie, aby zapewnić wysoką jakość paniki.

Pełna obsługa podłoża IC dostawca działa na zakłócenie dla każdego panelu i partii, aby zapewnić umieszczenie i kalibrację MEMS.

Wykończenia powierzchniowe i gotowość montażu

Końcowe wykończenie sprawia, że podłoże jest gotowe do wytrzymałych połączeń i długoterminowej niezawodności.

ENEPIG: Podobnie jak szlachetny, ale nadający się do łączenia drutu, flip-chip i BGA o drobnym szczeblu; fantastyczny dla tablic czujników MEMS i stosów hybrydowych.

A ścisłe podłoża IC producent łączy statystyczną kontrolę procesu z pełną śledzalnością partii w celu jednolitej wydajności MEMS i przyspieszonej analizy awarii.

podłoże IC Funkcje, które czynią nas wyjątkowymi

Oto krótki przegląd najbardziej uzależnionych funkcjonalności.

Przyspieszony NPI: Szybkie prototypy z tym samym oknem procesu jak produkcja masowa, przyspieszając rozwój MEMS bez utraty jakości.

Cięższa kontrola płaskości, zanieczyszczenia i hałasu elektrycznego jest wymagana dla MEMS niż dla zwykłych opakowań. A wyspecjalizowany podłoża IC producent zapewnia:

Produkcja podłoża IC obejmuje precyzyjne materiały, mikro wzory i rygorystyczne kontrole niezawodności: bardziej w przypadku MEMS.

Dobrze. podłoża IC producent może zapewnić wydajność poprzez zdyscyplinowaną konstrukcję stack-up, poprzez integralność, niskie straty miedzi i wytrzymałe wykończenia.

Z naciskiem na MEMS i integrację o wysokiej gęstości, klienci otrzymują stabilne zachowanie elektryczne, czysty montaż i niezawodną pracę w terenie.